# Performance Analysis of Dstatcom in Live Distribution System for Load Compensation

Nivedita Pande<sup>1</sup>, Priyanka Kubde<sup>2</sup>, Anushka Tekade<sup>3</sup>

<sup>1, 2, 3</sup>(Department of Electrical Engineering, Assistant Professor, Rajiv Gandhi College of Engineering & Research, India) Corresponding Author: Nivedita Pande

**Abstract:** Power Quality issues are the major concern in the low voltage distribution system. The paper suggests a shunt connected custom power device (DSTATCOM) to provide load compensation in the 3-phase, 4-wire network. The performance of the DSTATCOM is analyzed for two three leg VSI topologies; with single DC capacitor and with split DC capacitor under unbalanced and non-linear load. An Instantaneous Symmetrical Component Theory (ISCT) based Hysteresis Current Controller (HCC) has been introduced to generate switching pulses for VSI. A comparative analysis has been carried out for the DSTATCOM comprising of two VSI topologies on the basis of %THD and neutral current compensation. A DSTATCOM behavior using split DC capacitor topology is found to be more effective than VSI with single DC Capacitor. An extensive digital simulation is done using MATLAB/SIMULINK environment showing improved compensation performance.

*Keywords*– DSTATCOM, Hysteresis Current Controller, Instantaneous Symmetrical Component Theory, Nonlinear and unbalanced Load, Voltage Source Inverter (VSI)

Date of Submission: 16-04-2018

Date of acceptance: 04-05-2018

#### 1

#### I. Introduction

Good power quality means faultless power supply that has pure, noise-free and sinusoidal wave shape and is always within the voltage and frequency tolerance. Maintaining the power quality in the distribution system is a very difficult task because of increasing industrial and commercial power demand. The use of power electronics devices is increasing day by day, which leads to various power quality issues in the distribution network and thus degrading the system performance. Power quality issues can be mainly classified into two categories: Voltage based issues and current based issues. Current based issues include current harmonics, reactive power and excessive neutral current. To compensate these issues, many devices are available such as DVR and DSTATCOM. This paper suggests the use of DSTATCOM for the mitigating the current based issues. The main component of DSTATCOM is Voltage Source Inverter (VSI). A number of conventional VSI topologies for DSATCOM configuration are available such as Single DC capacitor VSI topology, Split DC Capacitor VSI topology and 4-leg VSI topology. Using DSTATCOM with single DC capacitor VSI topology does not compensate the neutral current. Therefore, for neutral current compensation a Split DC capacitor VSI topology is been used. This topology uses two common capacitors, with a center tap connected to the line neutral and thus providing a return path for neutral current. Four leg VSI topology can also be used to compensate neutral current as fourth leg provides return path for the neutral current with a single capacitor. However, maintaining the co-ordination between fourth leg and the other three legs of VSI becomes too complex in case of Four leg VSI.

As DSTATCOM injects current, Hysteresis Current Controller (HCC) is preferred to generate switching pulses for inverter. Hysteresis Current Controller requires reference current which is to be compared with the actual injected compensator current to generate the switching pulses. For this purpose, various reference current generation algorithms are available such as Instantaneous p-q Theory, Instantaneous Modified p-q Theory, Synchronous Reference Frame Theory, Instantaneous Symmetrical Component Theory and Vectorial Method. Among these, Instantaneous Symmetrical Component Theory (ISCT) is most preferred algorithm because of its simplicity of implementation.

This paper suggests the comparative analysis of two VSI topologies used for DSTATCOM with ISCT based Hysteresis controller. Among them split DC capacitor topology is found to be more effective for providing load compensation.

# **II.** System Configuration

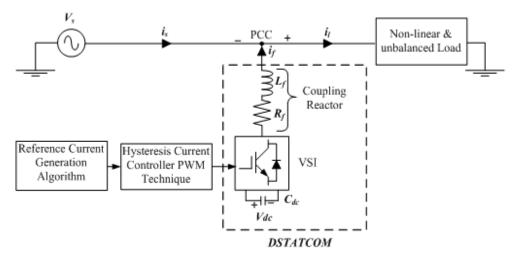

Fig.1. Single Line structure of DSTATCOM

A three phase, four wire system including a DSTATCOM configuration is shown in Fig.1. This paper presents a distribution system with non-linear and unbalanced load. Due to non-linear and unbalanced load, current based power quality issues are generated. To mitigate these issues, a DSTATCOM is used. The main component of DSATCOM is Voltage Source Inverter (VSI). Various topologies can be used for DSTATCOM configuration. The VSI topology is connected in shunt at the point of common coupling and through the interface reactor. In this stiff system, the non-linearity is introduced through a rectifier load. For creating switching pulses required for VSI, Hysteresis Current Controlled PWM technique is used to trigger switches. For Hysteresis Control Method, reference currents are required which can be acquired through various algorithms available among which ISCT is implemented for reference current generation. The system parameters are given in Table 1.

| TABLE 1 System Parameters |

|---------------------------|

|---------------------------|

| Supply Voltage      | Supply voltage of 230 V <sub>rms</sub> / phase, 50 Hz |  |  |  |  |  |

|---------------------|-------------------------------------------------------|--|--|--|--|--|

| R-L Load            | $R_a = 150\Omega$ $L_a = 100mH$                       |  |  |  |  |  |

|                     | $R_b = 75\Omega$ $L_b = 100mH$                        |  |  |  |  |  |

|                     | $R_c = 50\Omega$ $L_c = 10mH$                         |  |  |  |  |  |

| Non- Linear Load    | Three phase uncontrolled rectifier with               |  |  |  |  |  |

|                     | $R = 300\Omega, L = 100mH$                            |  |  |  |  |  |

| Interface Inductor  | $R_f=1\Omega, L_f=30mh$                               |  |  |  |  |  |

| Hysteresis band     | $\pm h = 0.08 \text{ A}$                              |  |  |  |  |  |

| PI controller gains | $K_p = 1, K_i = 0.5$                                  |  |  |  |  |  |

| DC Voltage          | V <sub>dc</sub> =500V(Single DC)                      |  |  |  |  |  |

|                     | V <sub>dc1</sub> =V <sub>dc</sub> =500V(Split DC)     |  |  |  |  |  |

| V <sub>dcref</sub>  | 510 V(Single DC), 1100V(Split DC)                     |  |  |  |  |  |

| DC Capacitor        | $C_{dc} = 2200 \mu F$ , Cdc1=Cdc2=2200 $\mu F$        |  |  |  |  |  |

# III. Conventional Visa Topologies For Low Voltage Distribution System 3.1 VSI with SINGLE DC CAPACITOR

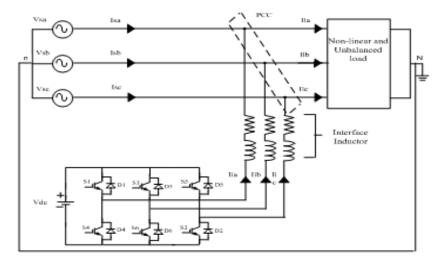

Fig.2. shows VSI with Single DC Capacitor which consists of six switches (S1-S6). A control scheme is required to operate the VSI switches. This paper reveals a hysteresis current controller which has been introduced for switching operation. In this topology, DSTATCOM is connected in shunt through interface

inductor at the point of common coupling (PCC). If loads are unbalanced and non-linear, the load currents will have a zero sequence component. In this topology, there is no return path provided for zero sequence of the current. Therefore, this topology cannot interject the current having a zero sequence component. Full compensation is not achieved as zero sequence components are not compensated. This shows the imperfection of single DC capacitor inverter.

Fig. 2. Single DC Capacitor VSI Topology

# 3.2 VSI WITH SPLIT DC CAPACITOR

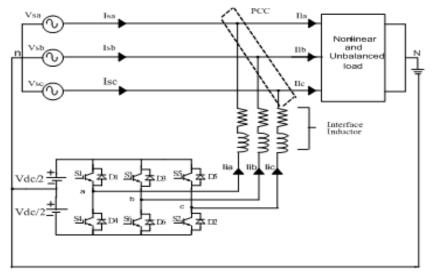

VSI with split DC Capacitor is given in the Fig.3. The neutral of the load and the source are connected together to the neutral of the Split DC Capacitor. There will be a return path for Zero Sequence component as shown in the Fig.3 that is path N-n. The Zero Sequence component will be compensated by the DSTATCOM as it is able to supply this component for unbalanced and non-linear load.

Here, the value of DC capacitor is taken to be 2200  $\mu$ F for simulation purpose. The value of capacitor can be increased up to the value of 10000  $\mu$ F without changing any parameters of the system except the voltage of DC Capacitor. It is selected in such a way that it will have lesser ripples. For better performance, the value of capacitor will increase in such a way that it acts as a battery and the proportional and integral gains of PI controller will have to be increased.

# **IV. Hysteresis Current Controller**

Hysteresis Current Controlled pulse width modulation is widely used because of its easy utilization, fast intense feedback with potential to limit peak current. This current controller is used to activate the switch of voltage source inverter. The objective of hysteresis current controller is to force the actual injected current to follow the reference quantity.

Fig.3 Split DC Capacitor VSI Topology

It starts to track the desired reference current from the point of common coupling. The logic equation of Hysteresis Current Controller can be given by-

I act >I ref + h then -1 I act < I ref -h then +1

The difference between the desired current  $i_{ref}$  and the injected current  $I_{actual}$  represents the error. When error reaches the lower limit, upper switches of inverter conducts and the current is forced to increase. When error reaches the lower limit, upper switches of inverter conducts and forces the current down.

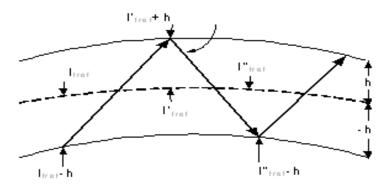

Fig.4. Hysteresis Current Controller

From Fig.4. dotted line represents the reference currents. The upper limit is created by adding hysteresis band to the reference currents i.e.  $(i_{ref}+h)$ . The lower limit is created by subtracting hysteresis band from the reference currents ( $I_{ref}-h$ ). The triangular wave depicts the actual hysteresis current. As the actual injected current exceeds the upper band i.e. ( $I_{ref}+h$ ), lower switches (2, 4, 6) conducts and as it crosses the lower band, i.e.( $i_{ref}-h$ ), upper switches (1,3,5) are conducted.

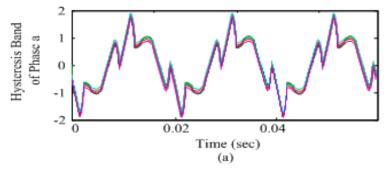

Fig.5. shows that the injected current produced by DSTATCOM follows the reference current which forms a Hysteresis Band of phase a. In essence, the inverter becomes a current source with a peak to peak current ripple. The current is controlled within the hysteresis band. The switching pulses  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$  and  $S_6$  are given to VSI to compensate the harmonic current produced by non-linear load.

Fig.5. Hysteresis Band of Phase a

#### V. Reference Current Generation

Mainly, the control algorithm used for the extraction of reference current components decides the performance and amount of benefits achieved by using DSTATCOM. There are various control algorithms available such as Instantaneous p-q Theory, Instantaneous Modified p-q Theory, Synchronous Reference Frame Theory, Instantaneous Symmetrical Component theory. Instantaneous p-q Theory requires transformation which increases control complexity of system.

Hence, the usage of Instantaneous Symmetrical Component Theory (ISCT) is preferred. ISCT is popular due to its easy implementation among the various control algorithms. It also does not require any transformation.

The purpose of compensation in 3-phase Four-wire system is to provide a balanced supply current in such a way that its zero sequence components are zero. Therefore,

$$i_{Sa} + i_{Sb} + i_{Sc} = 0 \tag{1}$$

The algorithm forces this source current to be unity power factor.

By assuming that the source voltages are balanced, they can be given by-

$$v_{Sa} = \sin \omega t$$

$$V_{Sb} = \sin \left( \omega t - 120^{\circ} \right)$$

$$V_{Sc} = \sin \left( \omega t + 120^{\circ} \right)$$

<sup>(2)</sup>

From symmetrical components,

$$\begin{bmatrix} V_{a0} \\ V_{a1} \\ V_{a2} \end{bmatrix} = \frac{1}{\sqrt{3}} \begin{bmatrix} 1 & 1 & 1 \\ 1 & a & a^2 \\ 1 & a^2 & a \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(3)

Therefore, the positive sequence component of source voltage  $V_{sa}$  will be,

$$V_{Sa_1} = \frac{1}{\sqrt{3}} \left\{ V_{Sa} + a V_{Sb} + a^2 V_{Sc} \right\}$$

(4)

$$a = e^{j120}$$

Where, And,  $e^{j\theta} = \cos \theta + j \sin \theta$

Therefore,

$$e^{j120} = \cos 120 + j \sin 120$$

=  $\frac{-1}{2} + j \frac{\sqrt{3}}{2}$  (5)

$$k_{4} = \left(i_{Sa} - \frac{1}{2}i_{Sb} - \frac{1}{2}i_{Sc}\right)$$

$$a^{2} = e^{j240} = \cos 240 + j\sin 240$$

$$= \frac{-1}{2} - j\frac{\sqrt{3}}{2}$$

(6)

Therefore,

$$V_{Sa1} = \frac{1}{\sqrt{3}} \left\{ V_{Sa} + \left(\frac{-1}{2}\right) V_{Sb} + j \frac{\sqrt{3}}{2} V_{Sb} + \left(\frac{-1}{2}\right) V_{Sc} + j \left(\frac{-\sqrt{3}}{2}\right) V_{Sc} \right\}$$

(7)

And as,  $\tan \delta = \frac{\sin \delta}{\cos \delta}$  Now, from equation (7) angle of the vector is given by

$$\delta = \angle V_{Sa1} = \tan^{-1} \left\{ \frac{\frac{\sqrt{3}}{2} V_{Sb} - \frac{\sqrt{3}}{2} V_{Sc}}{V_{Sa} - \frac{1}{2} V_{Sb} - \frac{1}{2} V_{Sc}} \right\}, \quad \delta = \tan^{-1} \left\{ \frac{\frac{\sqrt{3}}{2} (V_{Sb} - V_{Sc})}{\frac{3}{2} V_{Sa}} \right\}$$

(8)

By substituting the value of  $V_{sa}$ ,  $V_{sb}$  and  $V_{sc}$

$$\delta = \tan^{-1}\left\{\frac{-\cos\omega t}{\sin\omega t}\right\} = \omega t - \frac{\pi}{2}$$

(9)

From the power factor consideration, it is assumed that the phase of the vector is zero. Current lags that Vsa1 by an angle

$$\angle \left\{ V_{Sa} + aV_{Sb} + a^2 V_{Sc} \right\} = \angle \left\{ i_{Sa} + ai_{Sb} + a^2 i_{Sc} \right\} + \delta$$

$$\tag{10}$$

By substituting the values of a and  $a^2$  in equation 3,

$$\angle \left\{ \left( V_{Sa} - \frac{1}{2} V_{Sb} - \frac{1}{2} V_{Sc} \right) + j \frac{\sqrt{3}}{2} \left( V_{Sb} - V_{Sc} \right) \right\} = \angle \left\{ \left( i_{Sa} - \frac{1}{2} i_{Sb} - \frac{1}{2} i_{Sc} \right) + j \frac{\sqrt{3}}{2} \left( i_{Sb} - i_{Sc} \right) \right\} + \delta$$

(11)

After equating the angles,

$$\tan^{-1}\left(\frac{k_1}{k_2}\right) = \tan^{-1}\left(\frac{k_3}{k_4}\right) + \delta \tag{12}$$

Where, from equation

$$k_{1} = \frac{\sqrt{3}}{2} \left( V_{Sb} - V_{Sc} \right) , \quad k_{2} = \left( V_{Sa} - \frac{1}{2} V_{Sb} - \frac{1}{2} V_{Sc} \right) , \quad k_{3} = \frac{\sqrt{3}}{2} \left( i_{Sb} - i_{Sc} \right) , \quad k_{4} = \left( i_{Sa} - \frac{1}{2} i_{Sb} - \frac{1}{2} i_{Sc} \right)$$

$$(13)$$

Using formula,

DOI: 10.9790/1676-1302031828

$$\tan\left(\alpha+\beta\right) = \frac{\tan\alpha+\tan\beta}{1-\tan\alpha.\tan\beta} \tag{14}$$

Equation (14) can be expressed as,

$$\frac{k_1}{k_2} = \tan\left[\tan^{-1}\left(\frac{k_3}{k_4}\right) + \delta\right] \qquad \frac{k_1}{k_2} = \frac{\left(\frac{k_3}{k_4}\right) + \tan\delta}{1 - \left(\frac{k_3}{k_4}\right) \cdot \tan\delta}$$

(15)

Putting the value of  $k_1$  and  $k_2$  in above equation,

$$(V_{Sb} - V_{Sc} - 3\beta V_{Sa})i_{Sa} + (V_{Sc} - V_{Sa} - 3\beta V_{Sb})i_{Sa} + (V_{Sa} - V_{Sb} - 3\beta V_{Sc})i_{Sc} = 0$$

<sup>(16)</sup>

Where,

$$\beta = \frac{\tan \delta}{\sqrt{3}}$$

Here,  $\beta$  can be defined as the wanted fraction of average reactive power of load which is to be supplied by the Source. When the power factor angle is assumed to be zero, equation 6 implies that the instantaneous reactive power supplied by the source is zero.

When the angle is non-zero, the source supplies the reactive power that is equal to be  $\beta$  times the instantaneous power. The objective of the compensation is to supply the oscillating component such that the source supplies the average value of the load power.

$$V_{Sa}i_{Sa} + V_{Sb}i_{Sb} + V_{Sc}i_{Sc} = P_{l_{avg}}$$

(17)

Where, P<sub>lavg</sub> is a load power obtained by feeding the instantaneous load power to a low pass filter.

$$P_{l_{avg}} = V_{Sa} i_{Sa} + V_{Sb} i_{Sb} + V_{Sc} i_{Sc}$$

(18)

Since, the harmonic component in the load does not require any real power, the source only supplies the real power required by the load.

By combining equations (1), (16) and (17)

$$\begin{bmatrix} 1 & 1 & 1 \\ V_{Sb} - V_{Sc} - 3\beta V_{Sa} & V_{Sc} - V_{Sa} - 3\beta V_{Sb} & V_{Sa} - V_{Sb} - 3\beta V_{Sc} \\ V_{Sa} & V_{Sb} & V_{Sc} \end{bmatrix} \begin{bmatrix} i_{Sa} \\ i_{Sb} \\ i_{Sc} \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ P_{I_{avg}} \end{bmatrix}$$

(19)

By applying KCL at PCC

$$i_{refk} = i_{lk} - i_{sk}$$

(20)

Where k=a, b, c

Substituting above equation in equation

$$i_{a_{ref}} = i_{la} - i_{sa} \tag{21}$$

Hence, the reference compensator currents can be expressed as,

$$i_{a_{ref}} = i_{la} - \frac{V_{Sa} + (V_{Sb} - V_{Sc})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{b_{ref}} = i_{lb} - \frac{V_{Sb} + (V_{Sc} - V_{Sa})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sc}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sa} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sc} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sc} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sc} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sc} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sc} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sc} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sc} - V_{Sb})\beta}{V_{Sa}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc} + (V_{Sc} - V_{Sb})\beta}{V_{Sb}^{2} + V_{Sb}^{2} + V_{Sb}^{2}} P_{l_{avg}} \quad i_{c_{ref}} = i_{lc} - \frac{V_{Sc$$

# **VI. Simulation Results**

# 6.1 UNCOMPENSATED SYSTEM

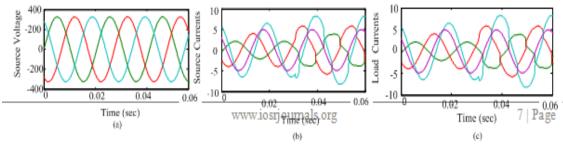

Simulation results of three-phase four wire distribution system without connecting DSTATCOM under non-linear and unbalanced load is depicted in Fig.6. The results are taken for transient condition by connecting non-linear load at 0.03 seconds. The source voltages are balanced and sinusoidal at both non-linear and unbalanced load as the system is stiff system as shown in Fig. 6(a). Due to unbalanced load, the magnitude unbalance can be observed in source currents and as non-linear load is connected at 0.03 sec, the unbalance as well as distortions can be seen in the source currents after 0.03sec. Fig. 6(b) and Fig. 6(c) shows non-linearity and unbalancing of the wave shape of source currents.

Fig.6. Uncompensated systems (a) Source Voltages (b) Source Currents (c) Load Currents

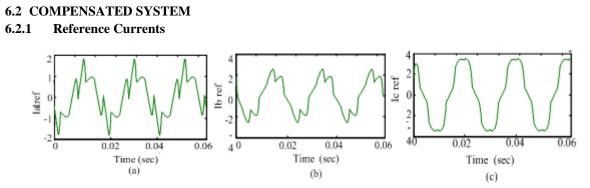

Fig.7 Reference Currents (a) Reference Current of Phase a (b) Reference Current of Phase b (c) Reference Current of Phase c

Reference currents of three phase a, b and c generated by ISCT theory is presented along with their tracking performance in Fig 7. The waveforms shown above are the reference currents which are to be followed by the currents injected by DSTATCOM to reduce non-linearity from the source currents. Thus, giving better tracking performance.

#### 6.2.2 Performance of DSTATCOM with Single DC Capacitor VSI

Fig.8. Single dc Capacitor VSI topology (a) Source Voltages (b) Load Currents (c) Injected Currents (d) Source Currents (e) Power Factor

The simulation results of DSTATCOM with single dc capacitor VSI under unbalanced and non-linear load are presented in Fig.8. Fig.8 (b) shows load currents which are unbalanced and distorted because of unbalanced and non-linear load. The compensator injected current by DSATCOM portrayed in Fig.8 (c) tracks the reference current during compensation. From Fig.8 (d) it can be seen that due to inappropriate compensation, source currents are neither balanced, nor-distortion free. It can be deduced from Fig.8 (e) that the power factor is not equal to unity.

The failure of the DSTATCOM to compensate the unbalanced non-linear loads is because the reference contains zero sequence components while the VSI unable to inject the currents having zero sequence component. This shows the unsatisfactory performance of DSTACOM and inadequacy to compensate zero sequence current. The sources power quality will deteriorate in all three phases for loads. Hence, this topology gives partial compensation.

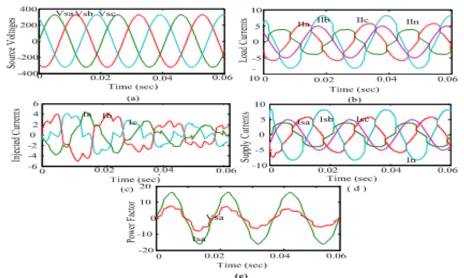

# 6.2.3 Performance of DSTATCOM with Split DC Capacitor VSI

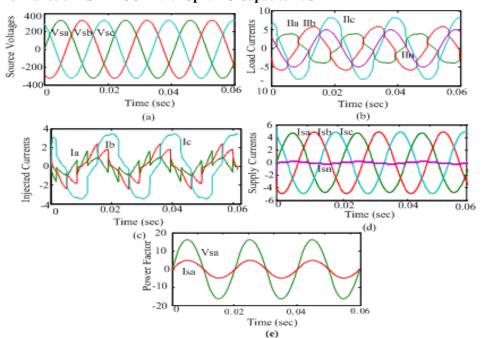

**Fig.9.** Split dc Capacitor VSI topology (a) Source Voltages (b) Load Currents (c) Injected Currents (d) Source Currents (e) Power Factor

|                    |                     | %THD  |       |       | Power Factor |       |       | Neutral Current |

|--------------------|---------------------|-------|-------|-------|--------------|-------|-------|-----------------|

|                    |                     | Phase | Phase | Phase | Phase        | Phase | Phase | In (A)          |

|                    |                     | а     | b     | с     | а            | b     | с     |                 |

| Uncompensated      | Single Dc Capacitor | 14.9% | 10.4% | 7.2%  | 0.995        | 0.95  | 0.998 | 2.958           |

| System             | Split DC Capacitor  | 14.9% | 10.4% | 7.2%  | 0.995        | 0.95  | 0.998 | 2.958           |

| Compensated System | Single DC Capacitor | 12.5% | 11.4% | 11.1% | 0.999        | 0.987 | 0.998 | 2.958           |

|                    | Split DC Capacitor  | 4.45% | 4.41% | 4.6%  | 1            | 0.99  | 1     | 0.098           |

**TABLE 2:** Comparative Analysis of DSTATCOM Performance

Simulation results of DSTATCOM with Split DC capacitor VSI topology are shown in Fig.9. From Fig.9 (c) it is seen that the reference and injected current are tracked in all the phases. The zero sequence current flowing into the neutral point of the dc capacitors through the path N-n. Hence zero sequence current will get path for compensation. Hence source currents are balanced and sinusoidal with zero neutral current and are in phase sinusoids with the respective source voltages deduced in Fig.9 (d) despite the load currents are unbalanced and distorted as shown in Fig.9 (b) under unbalanced and non-linear load. Thus, Power Factor becomes unity as presented in Fig.9 (e). From this simulation result, it can be observed that Split DC capacitor VSI topology gives effective performance in terms of neutral current compensation as compare to single DC VSI topology.

# VII. Conclusion

This paper discusses the use of DSTATCOM for load compensation with the help of two VSI topologies. Simulation is carried out in MATLAB/SIMULINK software. Incorporation of two VSI topologies shows that the split DC capacitor VSI topology is more efficient in terms of neutral current compensation and %THD. It gives better compensation under unbalanced and non-linear load condition. To attain the better compensation performance, ISCT based hysteresis current controller is working precisely. It is thus concluded that ISCT based hysteresis current controller with split DC capacitor VSI topology for DSTATCOM configuration is more efficient than single DC capacitor VSI topology under unbalanced and non-linear load condition.

#### References

- [1] A. Ghosh, G. Ledwich, "Power Quality Enhancement Using Custom Power Devices", Kluwer Academic Publisher, 2002.

- S. Iyer, A. Ghosh, A. Joshi, "Inverter topologies for DSTATCOM applications A simulation study", Elect. Power Syst. Res., vol.75, no. 2-3, pp. 161-170, Aug 2005.

- [3] N. Geddada, S. B. Karanki, M.K. Mishra, B.K. Kumar, "Modified four leg DSTATCOM Topology for compensation of Unbalanced and Non-linear loads in three phase four wire system", proceeding of European conference on Power electronics and applications (EPE), Sept 2011.

- [4] Ch. N. Reddy, B. V. Reddy, B. C. Babu, "Performance Analysis Of Differential Current Control Techniques For VSI Connected To R-L Load", International journal of engineering trends in engineering and development, issue 2, vol.5, pp 627-635, July 2012

- [5] N. K. Kummari, A. K. Singh, P. Kumar, "Comparative Evaluation of DSTATCOM Control Algorithms for Load Compensation", IEEE 2012

- [6] Arindam Ghosh, Avinash Joshi, "A New Approach to Load Balancing and Power Factor Correction in Power Distribution System", IEEE Transaction on power delivery, Vol. 15, no. 1, January 2000

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) is UGC approved Journal with Sl. No. 4198, Journal no. 45125.

-----

Nivedita Pande "Performance Analysis of Dstatcom in Live Distribution System for Load Compensation." IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) 13.2 (2018): 18-28.